近日,Amkor先进封装开发和集成副总裁 Michael Kelly与半导体工程公司坐下来讨论先进封装以及该技术面临的挑战。以下是该讨论的摘录。

SE:我们正处于一个巨大的半导体需求周期之中。是什么驱动了它?

Kelly:如果你退后一步,我们的行业一直是周期性的。然后,还有一些无关的因素,例如 Covid-19 和在家工作的经济。这有助于加剧这些芯片短缺。此外,人工智能是已成为我们行业重要驱动力的技术之一。它开始很小。这只是语音识别等数据中心所需的东西。现在,人工智能几乎无处不在,即使它只是一块硅片中某个位置的嵌入式内核,它可以帮助标准 GPU 更有效地渲染某种形状并具有预测能力。它可能用于平凡的事情,但它无处不在。人工智能的问题在于它需要大量的计算资源,用于算法训练和推理,这推动了高性能要求的发展。

SE:IC 封装并不新鲜,但几年前它主要是在后台。封装简单地封装和保护芯片。最近,封装变得更加重要。发生了什么变化?

Kelly:封装已经存在了很长时间。一直是这个东西通过电路板将现实世界连接到集成电路。您需要将来自硅的信号传递给人们可以用来创建产品的东西。封装简单地安装在电路板上。很长一段时间,半导体加工有了更多的发展。你有新的晶体管和架构。您有使用相同晶体管或更好晶体管来提高性能的新方法。这就是 50 多年来的故事。这就是关键技术的中心所在。它在芯片内部。随着时间的推移,更多的电子功能被内置在中央处理器内部和周围。然后,事情变得非常复杂。有不同的电压域和晶体管要求。然后我们遇到了一个新的关口。为了以合理的成本不断提高性能,您不能只将所有这些功能都放入尖端节点中相对较大的芯片中。因为晶圆会很贵。那就意味着即使您可以提高性能,但成本会以一种无法证明性能提升的方式上升。因此,您需要提出一个更好的经济模型来保持该性能成本比。一种方法是将高速资产(例如处理器内核)拉入前沿节点,并将其余芯片保留在其他节点上。通过以相同或更低的成本将混合节点的裸片组合在一个封装中,您可以获得相同的性能。所需的灵活性受到您所谈论的商业市场的影响。例如,我可以使用我在 10 种不同产品中设计的小芯片,并在封装级别以不同方式重新组合它们。那我就不需要全定制了这些产品中的每一种的片上系统(SoC) 设计。因此,封装是将所有部分组合在一起的小信封,使这些异构结构更加强大。因此,与每次都进行定制设计相比,您的产品上市时间更短。

SE:其他问题是什么?

Kelly:有些公司没有足够的设计师来为所有市场设计定制的 SoC。但是,如果我设计小芯片,然后将它们混搭到不同的细分市场,那将更好地发挥我的设计才能。封装在这里混合在一起。因此,如果您分解 SoC,则需要在封装级别重新聚合 IP 块,才能拥有功能齐全的产品。这推动了软件包做更多的事情。您需要细线来保持集成。您需要管理热废热或电力。您需要为越来越耗电的设备供电。这对包装提出了额外的要求。

SE:这里最大的担忧是什么?

Kelly:功耗是很大的挑战。由于封装级别的集成,它在封装行业受到欢迎。不幸的是,硅会产生大量废热。它的热效率不高。你需要把热量倒在某个地方。我们必须以我们可以参与的方式参与,这是在芯片和封装边缘之间。对于在最终产品中进行散热的任何人,无论是在手机壳中还是在数据中心的水冷却器中,我们都必须使其尽可能具有热效率。我们必须为高性能封装提供多少实际电流也变得有趣。功率没有下降,但电压正在下降。为了提供相同的总功率或更多功率,我们的电流正在上升。像需要解决电迁移问题。我们可能需要在封装中进行更多的电压转换和电压调节。这样,我们可以将更高的电压带入封装,然后将它们分成更低的电压。这意味着我们不必将尽可能多的总电流拖入封装。因此,电能以两种方式打击我们。这是热量,但它也在以电力方式管理电力输送网络。这迫使更多的内容进入封装,同时也在热功耗方面尽力而为。

SE:还有其他挑战吗?

Kelly:我们开始看到很多异构集成设计。我们只是看到的一角。随着我们进一步研究,与最终产品所需的同步的强度也在加快。您需要了解如何投资异构技术。这样,您可以覆盖尽可能多的应用。您还需要保持在或高于技术曲线,以便在这个激进的异构封装空间中跟上并挑战您的竞争对手。

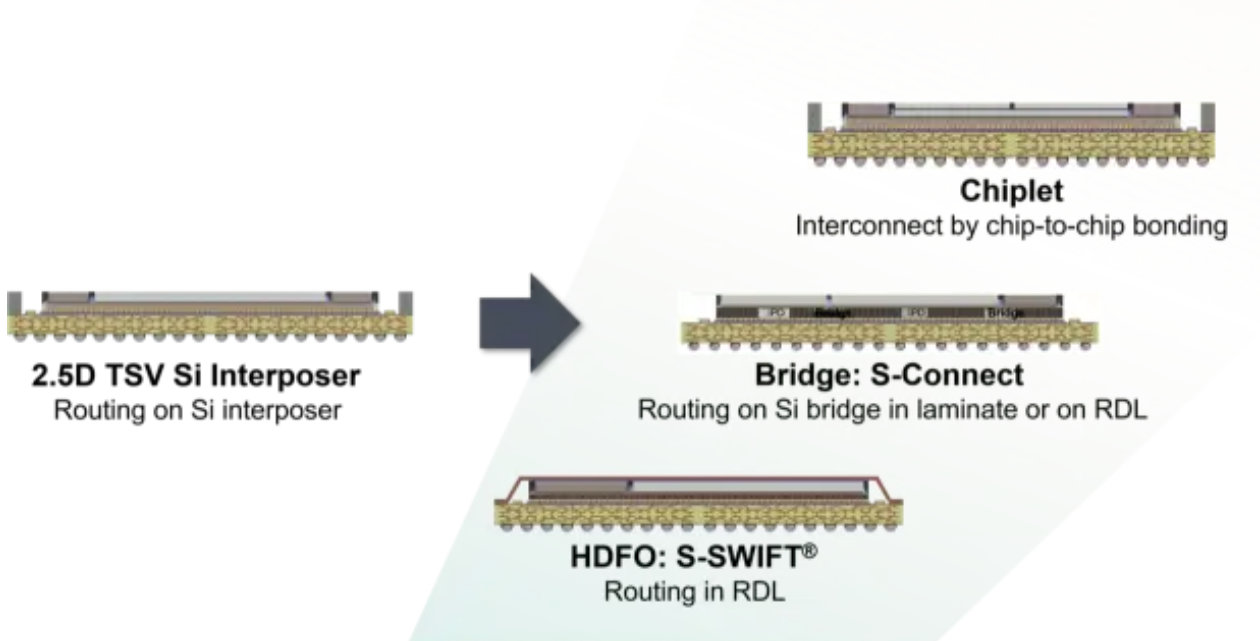

图 1:2.5D 封装、高密度扇出 (HDFO)、桥接封装和小芯片示例。资料来源:安靠

SE:扇出式封装正在流行起来。在扇出的一个示例中,DRAM die堆叠在封装中的处理器上。什么是扇出封装,它有什么承诺?

Kelly:当你在谈论扇出时,它有助于将其分为两部分。有低密度扇出。然后是高密度扇出,这是一种更现代的集成多个裸片或异构集成的创新。低密度扇出已经存在了很长一段时间。它具有良好的电性能。它往往具有低层数。封装也可以很薄。低密度扇出非常适合许多产品,尤其是移动产品。然后是我所说的高密度扇出。这包含相同的铜和电介质,但我们正在将它们成像到线条和空间方面更精细的几何形状。它有多层带有微小的通孔。高密度扇出已成为整个异构宇宙中如何将小芯片集成到更大模块中的竞争者。

SE:扇出和其他封装具有重新分布层 (RDL),它们是将一个裸片电连接到封装的另一部分的微小金属迹线。RDL 的线和空间尺寸是多少?

Kelly:如果你在谈论高密度扇出,2μm 线路和 2μm 空间是今天的最佳选择。代工厂和OSAT可以达到2μm-2μm。一旦低于 2μm-2μm 或 1.5μm-1.5μm,您就会看到制作痕迹的方式略有不同。但它在很大程度上是相同的电介质和铜。许多公司正在研究亚 1μm 线/空间。这些几何形状将是未来的路径。它归结为产品需要什么。在接下来的几年里,2μm-2μm 将成为很多产品的最佳选择。但随着间距超过 40μm,将面临添加更多层和/或更小的线、空间和通孔的压力。

SE:扇出封装容易发生芯片移位和翘曲。这里发生了什么事?

凯利:在过去,压力是封装业存在的祸根。那还在那里。新型单芯片和多芯片封装的最大挑战之一是翘曲。不幸的是,硅的热膨胀系数约为 2。每加热或冷却 1 摄氏度,它的膨胀系数就是百万分之二。我们在它周围使用的所有有机材料都是 10 或更大。当它们在一个包装中彼此紧密接触,并且它被加热或冷却时,你正在不同地膨胀和收缩,这取决于你在堆栈中的位置。那就是让事情脱离平面。没有扁平封装之类的东西。它有某种翘曲或弯曲。它可能肉眼看不到,但它始终存在。这也增加了压力。翘曲是我们必须管理的。如今,我们有很好的工具来管理它。与 10 年前相比,我们有更好的材料选择。管理给定尺寸的翘曲变得越来越容易,但同时尺寸也在增加。所以我们在追逐一个移动的目标。

SE:扇出封装现在包含高带宽内存 (HBM)。您可以在扇出中加入多少个 HBM?

凯利:两个或四个HBM都没问题。当你变大时,你必须担心翘曲。您必须担心在模块中移动压力。问题是,你能控制翘曲吗?你能管理权力吗?你能保持所有调制器连接在一个有意义的音高上吗?你能管理大电流和电迁移吗?当你变得更大时,挑战并不是线性增加的。它更像是一个渐近增加。

SE:2.5D呢?

Kelly:2.5D是高端AI产品的中流砥柱,尤其是GPU。这是一个庞大且不断增长的市场。2.5D 用于数据中心以获取 zettabytes 数据并针对其算法运行以改进算法。当您在手机上的语音识别效果更好时,并不是因为您的手机变得更好。这是因为这些高端的人工智能 GPU 可以处理更多的数据并且算法更好。所有这些培训都在数据中心进行。

SE:在 2.5D/3D 和其他封装中,有很多关于标线尺寸的讨论。这意味着什么?

Kelly:通常,当人们说掩模版尺寸时,他们指的是半导体晶圆厂掩模版尺寸。当您谈论 3X 或 4X 封装中的标线尺寸时,这是一个关于插入器可能有多大的术语。在 2.5D 中,您可能有两个或四个 ASIC。6 个 HBM 是比较主流的。你可以看到八个,也许是 10 个 HBM。它会在那里达到顶峰。这不仅仅是你在封装中获得了多少 HBM,还包括封装的有效性。也许你最好把那个巨大的 2.5D 包放在两个包中。然后,您需要找到一种方法来做到这一点,并查看所有系统挑战,例如热力和电力管理。

SE:2.5D还有其他问题吗?

凯利:它们很大。内插器它本身就是一块技术含量相对较低的硅片。它上面有物理路由。然后,如果它是一个大功率设备,你可以将这些中介层与嵌入式电容器结合起来。这有助于管理输入芯片的电压功率。内插器总是有点挑战,因为很难找到内插器的来源。代工厂内的中介层可用性是有限的。制造 5nm 芯片可以比插入器赚更多的钱。从经济上讲,对于晶圆厂来说,这不是一个好生意。该晶圆厂希望销售高端硅。问题是我们是否会从硅中介层转向基于 HBM 的产品的有机中介层?它们在供应链中更容易获得。还是我们会继续使用硅?陪审团还在外面。有一段时间,它将是硅。这是可靠的。它很健壮。这些是最终客户不一定想弄乱的长期产品,因为它们可以工作。

SE:您认为 HBM3 即将推出 2.5D 吗?

凯利:处于人工智能前沿的人们已经在努力准备这些产品。

SE:小芯片在哪里适合?

凯利:对我来说,小芯片就是你从单个SoC中取出一个或多个片段,然后分解一些功能块或功能块的集合,这些功能块或功能块的集合原本是离散 SoC 的一部分。然后,必须在封装级别重新集成小芯片。

SE:我们已经看到一些公司使用 die-to-die 互连开发类似小芯片的设计,对吧?

凯利:这里有两个方向。首先,有些公司在这个竞争激烈的市场中处于领先地位。你有像 AMD、英特尔和其他一些公司这样的领导者。他们在自己的 die-to-die 小芯片总线接口上投入了大量资金。其中一些是专有的。这些设计给了他们竞争优势。他们不会确切地告诉世界其他地方他们是如何做他们的小芯片接口的。在这个竞争激烈的高性能市场中,他们需要这种优势。还有另一个方向,有很多产品需要从现在的 SoC 迁移。也许他们是一年或几年的时间。出于与其他人相同的原因,他们也将需要小芯片。他们需要在工程资源有限的上市时间环境中管理成本。

SE:另一个阵营需要多种技术来启用小芯片。例如,要将封装中的一个小芯片连接到另一个小芯片,它们将需要芯片到芯片的互连,对吗?

Kelly:Open Domain-Specific Architecture (ODSA) 子项目提供了开源 die-to-die 技术。多家公司正在共同努力。这些技术非常具有竞争力,这意味着它们有足够的带宽来支持各种小芯片架构。它们足够灵活,可以支持细间距,如果是 MCM(多芯片模块),甚至可以支持更大的间距。再一次,将有两个层次。顶层正在开发他们自己的 die-to-die 接口,这些接口大多是专有的。然后,您将拥有一个不断发展的世界,由于其自身的性能、成本和上市时间的原因,需要小芯片。

SE:未来,假设一家公司希望与 OSAT 合作,使用这些接口开发小芯片设计。这将如何发展?

凯利:总线选择、总线认证和总线设计将始终存在于 ASIC 或处理器设计社区中。未来,假设商家交易所足够开放,人们可以从商店采购物理硅。然后,你需要构建原型,所以你去OSAT. 这可能是您将来可以看到的商业模式。但它比这复杂得多,因为它需要巨大的仿真能力来确保在您的设计阶段一切正常。我们的客户现在这样做了,尽管我们已经看到一些客户来找我们,要求对产品进行更全面的电气验证。这是一个缓慢增长的趋势。我提到了两个层次。随着第二层开始开发更多产品,我们可能会看到更多的设计周期在 OSAT 内部进行。

SE:还需要发生什么?

凯利:我们知道这些总线类型。作为 OSAT,我们需要了解的是需要什么样的封装技术才能将其连接起来并使其工作。通常它归结为几个简单的事情——凸块尺寸、凸块间距、线宽、通孔,也许还有层数。所以我们需要了解这些总线以及它们如何影响封装。归根结底,我们实际上并没有进行电气设计,但随着时间的推移,我们会看到更多。从本质上讲,OSAT 不会关心 die-to-die 接口是 XSR、AIB 还是其他什么,只要您提前开发了需要的东西。需要一两年的时间才能使封装取得重大进展并做好准备。

SE:混合键合呢?OSAT 能做到这一点吗?

凯利:当然。我们正在接近您可以购买该技术的地步。通过一些投资和你自己的发展,你可以到达那里。因此,OSAT 做到这一点并不存在巨大的技术障碍。这取决于什么是有效的商业案例,它会迫使 OSAT 进入该业务。我们正在深入了解这项技术。

SE:封装行业是否需要新的突破?

凯利:我希望有人能发明一种基于 CTE 更高的硅。这对我们有很大帮助。如果我们有更低的压力以及来自彼此更接近的不同材料的 CTE,我们将面临今天在封装中面临的一半挑战。硅很复杂。它是高 CTE 金属和有机材料与低 CTE 体硅的混合物。这是一个非常不均匀的系统。你从这个块状硅硅片开始,然后你几乎可以处理堆栈中的所有东西。所以它在机械上更具可预测性。如果我们能够提出能够缩小硅之间 CTE 差异的材料组,那么更大的系统将更容易实现。翘曲不会那么具有挑战性。压力会更低。可靠性会更好。成本目标将更容易实现。

版权及免责声明:凡本网所属版权作品,转载时须获得授权并注明来源“物联之家 - 物联观察新视角,国内领先科技门户”,违者本网将保留追究其相关法律责任的权力。凡转载文章,不代表本网观点和立场。

延伸阅读

版权所有:物联之家 - 物联观察新视角,国内领先科技门户