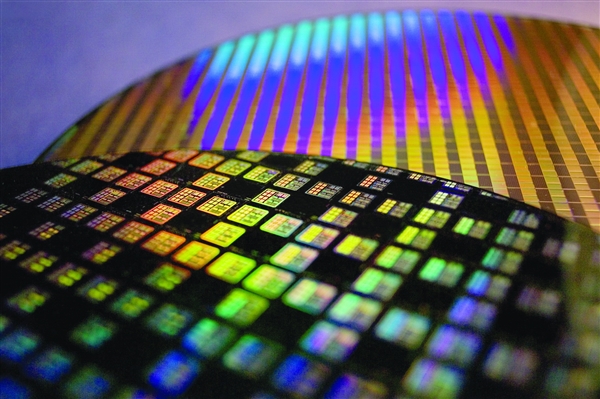

台积电是第一家将EUV(极紫外)光刻工艺商用到晶圆代工的企业,目前投产的工艺包括N7+、N6和N5三代。

其中N7+即第二代7nm,EUV总计4层。即便如此,这也相较于多重曝光也节省了时间,提高了芯片的生产效率。

不过,迭代到5nm后,EUV的层数达到了14层,包括但不限于触点、过孔以及关键金属层等过程。

而最快2022年投产的3nm,为了实现15%的性能提升、30%的功耗下降以及70%的密度增加,ASML(阿斯麦)透露,EUV将超过20层,也就是鳍片和栅极都要引入EUV切割掩模。

阿斯麦CEO Peter Wennink表示,EUV层数增加有很多好处,比如只需要单重曝光而不是DUV设备的多重曝光,对DRAM芯片同样如此。

为此,台积电将需要确保EUV光刻机的安装数量,但他们显得非常有信心。

版权及免责声明:凡本网所属版权作品,转载时须获得授权并注明来源“物联之家 - 物联观察新视角,国内领先科技门户”,违者本网将保留追究其相关法律责任的权力。凡转载文章,不代表本网观点和立场。

延伸阅读

版权所有:物联之家 - 物联观察新视角,国内领先科技门户