代工厂、设备供应商、研发机构等都在研发一种称之为铜混合键合(Hybrid bonding)工艺,这项技术正在推动下一代2.5D和3D封装技术。与现有的堆叠和键合方法相比,混合键合可以提供更高的带宽和更低的功耗,但混合键合技术也更难实现。

异构集成是铜混合键合的主要优势

铜混合键合并不是新鲜事,从2016年开始,CMOS图像传感器开始使用晶圆间(Wafer-to-Wafer)的混合键合技术制造产品。具体而言,供应商会先生产一个逻辑晶圆,然后生产一个用于像素处理的单独晶圆,之后使用铜互连技术将两个晶圆结合在一起,再将各芯片切成小片,形成CMOS图像传感器。

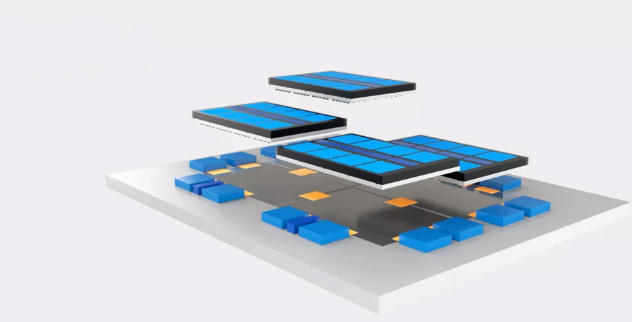

混合键合与先进封装的工作方式几乎相同,但前者更复杂。供应商正在开发另一种不同的变体,称为裸片对晶圆(Die-to-Wafer)的键合,可以在内插器或者其他裸片上堆叠和键合裸片。KLA的行销高级总监Stephen Hiebert表示:“我们能观察到裸片对晶圆的混合键合发展强劲,其主要优势在于它能够实现不同尺寸芯片的异构集成。”

这一方案将先进封装提高到一个新的水平,在当今先进封装案例中,供应商可以在封装中集成多裸片的DRAM堆栈,并使用现有的互连方案连接裸片。通过混合键合,DRAM裸片可以使用铜互连的方法提供更高的带宽,这种方法也可以用在内存堆栈和其他高级组合的逻辑中。

Xperi的杰出工程师Guilian Gao在最近的演讲中说:“它具有适用于不同应用的潜力,包括3D DRAM,异构集成和芯片分解。”

不过这是一项极具挑战性的工作。裸片对晶圆的混合键合需要原始的芯片、先进的设备和完美的集成方案,但是如果供应商能够满足这些要求,那么该项技术将成为高级芯片设计的诱人选择。

传统上,为改进设计,业界开发了片上系统(SoC),可以缩小每个具有不同功能的节点,然后在将它们封装到同一裸片上,但是随着单个节点正变得越来越复杂和昂贵,更多的人转向寻找新的替代方案。在传统的先进封装中组装复杂的芯片可以扩展节点,使用混合键合的先进封装则是另一种选择。

GlobalFoundry、英特尔、三星、台积电和联电都在致力于铜混合键合封装技术,Imec和Leti也是如此。此外,Xperi正在开发一种混合键合技术,并将该技术许可给其他公司。

已有IC封装技术的特色

IC封装类型众多,细分封装市场的互连类型,包括引线键合、倒装芯片、晶圆级封装(WLP)和直通硅通孔(TSV)。互连是将一个芯片连接到封装中的另一个芯片,TSV的I/O数量最高,其次是WLP、倒装芯片和引线键合,混合互连比TSV密度更高。

TechSearch称 ,当今的封装大约有75%至80%是基于引线键合,即使用焊线机细线将一个芯片接到另一个芯片或基板上,引线键合多用于商品包装和存储器裸片堆叠。

在倒装芯片中,使用各种工艺步骤在芯片顶部形成大量的焊料凸块或微小的铜凸块,然后将器件翻转并安装在单独的芯片或板上。凸块落在铜焊盘上,形成点连接,称之为晶圆键合机的系统键合裸片。

WLP是直接在晶圆上进行封装测试,之后再切割成单颗组件。扇出晶圆级封装(Fan-out WLP)也是晶圆级封装中的一种。Veeco的一位科学家Cliff McCold在ECTC的演讲中说,“采用WLP能够进行较小的二维连接,从而将硅芯片重新分派到更大的面积上,为现代设备提供更高的I/O密度,更高的带宽和性能。”

TSV用于高端2.5D/3D封装。在2.5D封装中,裸片堆叠在内插器上,内插器中包含TSV,中间层是连接芯片和电路板之间的桥梁,可提供更多的I/O和带宽。

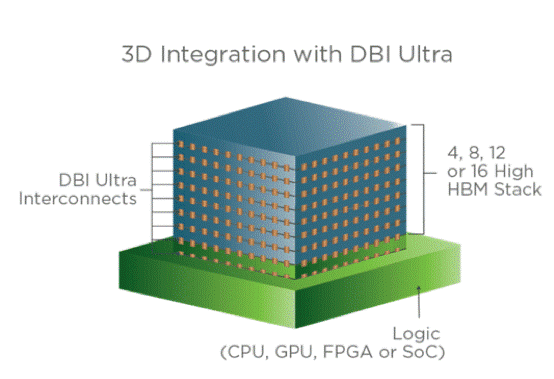

2.5D封装和3D封装的类型众多,高带宽存储器(HBM)就是一种3D封装类型,这一方法是将DRAM裸片堆叠在一起。将逻辑堆叠在逻辑上或将逻辑置于内存上的方法也正在出现。英特尔产品集成总监Ramune Nagisetty表示,逻辑堆叠在逻辑上的方法还没有普及,逻辑堆叠在内存上的方法目前正在兴起。

在封装中,目前备受关注的是小芯片。小芯片本身不是一种封装类型,但芯片制造商的库中可以拥有一个模块化裸片或多种小芯片,客户可以混合搭配这些芯片,并使用封装中裸片对裸片(Die-to-Die)的互连方案进行连接。

小芯片可以存在于现有的封装类型或新的体系架构中。“这是一种架构方法,” UMC(联华电子)负责业务开发的副总裁Walter Ng说,“它正在为任务需求优化解决方案,这些需求包括速度、热量、功率等性能,有时还需要考虑成本因素。”

当下最先进的2.5D封装和3D封装是供应商所使用的现有互连方案和晶圆键合器。在这些封装中,使用铜凸块或铜柱堆叠和连接裸片,基于焊接材料,凸块和支柱在不同的设备之间提供小而快速的电气连接。

最先进的微型凸块的间距是40μm至36μm,这里的间距包括一定的空间距离,例如40μm间距就是25μm的铜柱加上15微米的空间距离。

对于细间距的要求,业界使用热压缩连接(TCB)。用一个TCB键合器取出一块裸片,并将其凸块与另一块裸片的凸块对齐,再用压力和热力将凸块键合起来。不过,TCB过程缓慢,且铜凸块也正在逼近物理极限。一般而言,视极限间距为20μm,但也有一部分人在尝试延伸凸点间距。

Imec正在开发一种使用TCB实现的10μm间距技术,7μm和5μm也正在研发中。“40μm凸块间距有足够的焊接材料来补偿电流变化。当缩放到10μm或更小的间距时,情况将会发生变化,” Imec的高级科学家Jaber Derakhshandeh在最近的ECTC会议上的一篇论文中说,“在细间距的微泵中,电流量和良好的连接取决于TCB工具的精度、错位、倾斜以及焊料的变形量。”

为了延长微型凸块的发展寿命,Imec开发了一种金属垫板工艺,同以前一样,裸片上仍然有微型凸块,不同的是,在Imec工艺中,裸片上还有假金属微凸块,这类凸块类似于支撑架构的小梁。

Derakhshandeh说:“在3D裸片对晶圆的堆叠中引入了一个假金属微凸块,以减小TCB工具的倾斜误差,并控制焊料变形,从而使粘合裸片不同位置的电阻和成形接头的质量相同。”。

混合键合是TCB的补充

在某些时候,微型凸块/支柱和TCB可能会用光,这时候就需要混合键合,它可以用在微凸技术碰壁后或者在此前插入。

不过微型凸块不会很快在市场上消失,微型凸块和混合键合技术都将在市场上占据一席之地,这取决于具体的应用。

目前混合键合技术正在发展,台积电最有发言权,其正在研究一种叫做集成芯片系统(SoIC)的技术。使用混合键合,台积电的SoIC技术可以实现低于微米的键合间距。据悉,SoIC的缓冲垫间距是现有方案的0.25倍。高密度版本可以实现10倍以上的芯片到芯片的通信速度,高达近2000倍的带宽密度和20倍的能源效率。

台积电的SoIC计划于2021年投入生产,可以实现小间距HBM和SRAM存储立方体以及类似3D的芯片架构。台积电研究员MF Chen在最近的一篇论文中说,与当今HBM相比,“继承了SoIC的DRAM存储器立方体可以提供更高的存储器密度、带宽和功率效率。”

台积电正在开发芯片对晶圆(Chip-to-Wafer)的混合键合技术。晶圆键合已经在微机电系统(MEMS)和其他应用中使用多年,且类型众多。“微电子和微机电系统的制造和封装依赖于两个基板或晶片的键合,” Brewer Science的高级研究化学家Xiao Liu说道,“在微机电系统的制造过程中,器件晶圆将被粘合到另一个晶圆上,以保护敏感的MEMS结构。直接键合技术(例如熔融键合和阳极键合)或间接键合技术(例如金属共晶、热压键合和胶粘剂键合)都是常用的方法。使用胶粘剂作为两个基板之间的中间层,处理会更加灵活。”

铜混合键合最早出现在2016年,当时索尼将这项技术用于CMOS图像传感器, 索尼从现在属于Xperi的Ziptronix获得了该技术的许可。

Xperi的技术称为直接绑定互连(DBI),DBI在传统的晶圆厂中进行,并应用于晶圆对晶圆的键合工艺,在这一过程中,先对晶圆进行处理,然后将金属焊盘凹入表面,使表面变得平滑。

分离晶圆也经历类似的过程,晶片使用两步工艺键合,首先是电介质互连,然后是金属互连。

EV Group业务发展总监Thomas Uhrmann表示:“总体而言,晶圆对晶圆是设备制造的首选方法,在整个工艺流程中,晶圆都保留在前端晶圆厂环境中。在这种情况下,用于混合键合的晶圆制备在界面设计规则、清洁度、材料选择以及激活和对准方面面临诸多挑战。氧化物表面上的任何颗粒都会产生比颗粒本身大100至1,000倍的空隙。”

尽管如此,该技术已被证明可用于图像传感器,其他设备正在研究开发中。Uhrmann说:“计划进一步推出诸如堆叠SRAM到处理器芯片之类的器件。”

混合键合的3D集成,图片源自:Xperi

铜混合键合推动先进封装

对于先进芯片封装,业界还致力于裸片对晶圆和裸片对裸片的铜混合键合,即将裸片堆叠在晶圆上、将裸片堆叠在中介层上或将裸片堆叠在裸片上。

这比晶圆间键合更加困难。“对于裸片对晶圆的混合键合而言,处理不带颗粒的裸片的基础设施以及键合裸片的能力成为一项重大挑战。” Uhrmann说,“虽然可以从晶圆级复制或改写芯片级的界面设计和预处理,但在芯片处理方面仍存在许多挑战。通常,后端工艺(例如切块、裸片处理和在薄膜框架上的裸片传输)必须适应前端清洁级别,才能在裸片级别获得较高的粘合率。”

Uhrmann说,“晶圆对晶圆的键合方式正在发展,当我看到这种方式的过程时,看到工具开发的方向时,我认为这是一项非常复杂的集成任务,但是台积电这样的公司正在推动这个行业的发展,我们可以对其抱有期待。”

封装的混合键合与传统的IC封装在某些方面是不同的。传统上,IC封装是在一个OSAT(Outsourced Semiconductor Assembly and Test,委外封测代工厂)或封装厂中进行的,而铜混合键合却是在晶圆厂的洁净室中进行,而不是OSAT中。与传统封装处理尺寸缺陷不同,混合键合对微小的纳米级缺陷非常敏感,需要工厂级的洁净室来防止微小缺陷干扰生产过程。

缺陷控制至关重要。赛博光学研发副总裁Tim Skunes说,“考虑到这些工艺使用已知的昂贵优良裸片,失败成本很高。在组件之间,有一些突起形成垂直的电气连接,控制凸块高度和共面性对于确保堆叠组件之间的可靠性至关重要。”

事实上,已知良好模具(KGD)至关重要。KGD是符合给定规格的未包装零件或裸片,如果没有KGD,封装可能遭受低产或失败。

KGD对封装厂也很重要。“我们收到裸片,对其进行封装,并交付功能产品,合作方会要求我们提供非常高的产量。”东方电气工程技术营销总监曹丽红在最近的一次活动中表示,“因此,我们希望KGD能够经过充分测试并功能良好。”

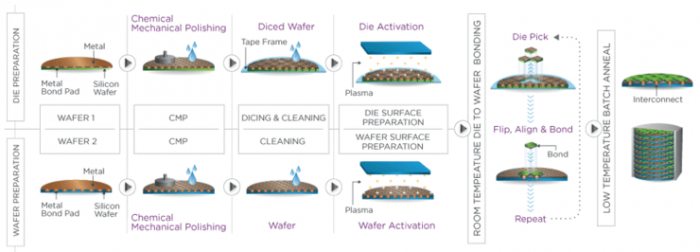

裸片对晶圆的混合键合类似于晶圆对晶圆的工艺。最大的区别在于芯片是用高速倒装芯片键合器中检测或在其他芯片上切割和堆叠的。

Xperi的裸片对晶圆混合键合流程图,图片源自:Xperi

整个过程从晶圆厂开始,使用各种设备在晶圆上加工芯片,这部分被称之为前段生产新(FEOL)。在混合键合中,两个或更多的晶圆在流动过程中被加工。之后,晶圆被运送到生产线后端(BEOL)的特殊部分,使用不同的设备对晶圆进行单一镶嵌工艺。

单一镶嵌工艺是一项成熟的技术,通常是将氧化物材料沉淀在晶圆上,然后用微小的通孔对氧化物材料进行蚀刻并绘制图案,最后通过沉积工艺填充铜,继而在晶圆表面上形成铜互连或焊盘,铜焊盘以微米为单位,相对较大。这一过程与当今先进的晶圆厂芯片生产类似,但对于高级芯片而言,最大的区别在于铜互连是纳米级别的。

上述流程就是Xperi的新裸片对晶圆的铜混合键合工艺的最初模式,其他公司使用类似或有细微不同的流程。

Xperi晶圆对晶圆工艺的第一步是使用化学机械抛光(CMP)抛光晶圆表面,即通过化学方法和机械方法抛光表面。在这一过程中,铜焊板略微凹陷在晶圆表面,得到浅而均匀的凹槽,有较好的良率。

不过,化学机械抛光(CMP)实现过程困难,抛光过度会使铜焊盘的凹槽太大,最终可能导致某些焊盘无法接和,抛光不足则会留下铜残留物造成短路。针对这一问题,Xperi开发出200nm和300nm CMP功能。Xperi工程部副总裁Laura Mirkarimi表示:“在过去十年中,CMP技术在设备设计、材料选择和监控方面都进行了创新,能够达到精准控制,让过程可重复且具有稳定性。”

在经过CMP之后,需要使用原子力显微镜(AFM)和其他工具对晶圆表面进行测量,这一部分非常关键。

KLA的Hiebert说:“对于混合键合,测量镶嵌焊盘形成后的晶圆表面必须采用亚纳米精度,以确保铜焊盘苛刻的凹凸要求。铜混合键合的主要工艺挑战包括晶圆表面缺陷控制、晶圆表面轮廓纳米级控制以及控制顶部和底部芯片上的铜焊盘的对准。随着混合键距变小,例如晶圆对晶圆间距小于2μm或裸片对晶圆间距小于10μm,这些表面缺陷、表面轮廓和键合焊盘对准挑战变得更加重要。”

不过这可能还不够,在某些时候,还会考虑到探测。FormFactor高级副总裁Amy Leong表示:“传统上认为直接在铜焊盘或铜凸块上进行探测是不可能的,如何在探针尖端和凸块之间保持稳定的电接触是需要关注的重点。”

为此,FormFactor开发了一种基于MEMS的探针设计,称为Skate。结合低接触力,尖端会轻柔地穿过氧化层,从而与凸块形成电接触。

完成计量步骤后,还需要对晶圆进行清洁和退火处理,然后再使用刀片或隐形激光切割系统在晶圆上切割芯片,这将产生用于封装的单个裸片。裸片切割极具挑战性,若切割不当则会产生颗粒、污染物和边缘缺陷。

KLA的Hiebert说:“对于裸片之间的混合键合,晶圆切割和裸片处理增加了额外的颗粒生产源,必须对其进行管理。由于晶圆的污染程度低得多,因此正在研究对晶圆对晶圆进行离子切割的混合键合方案。”

切割之后是粘合,这一步骤需要使用倒装芯片键合机直接从切割框架中拾取芯片,然后将芯片放置在主晶圆或其他芯片上,这两个结构在常温下立即结合。在铜混合键合中,芯片或晶圆先使用电介质键合,再进行金属互连。

粘合过程对粘合剂的对准精度提出挑战,在某些情况下,对准精度需要达到几微米,业界一般需要达到亚微米级别。

“尽管裸片的对准是一项挑战,但倒装芯片键合机已经向前迈了一大步,”EV Group的Uhrmann说:“晶圆间键合正朝着覆盖层小于100nm的方向发展,因此符合先进节点的要求。对于裸片对晶圆,通常精度和生产量之间存在依赖关系,其中较高的精度可以通过较低的总体生产量来平衡。由于工具已经针对诸如焊接和热压连接之类的后端工艺进行了优化,因此1μm的规格在很长一段时间能都是足够的。混合式芯片对晶圆键合改变了设备设计,这是由精度和设备清洁度引起的,下一代工具的规格将远远低于500nm。”

业界正在为这一目标而努力,在ECTC上,BE半导体公司(Besi)展示了一种新的混合芯片-晶圆键合机原型的第一项成果,最终规格目标为200nm、ISO 3洁净室环境以及2000 UPH的300 mm晶圆基板。该机器包括零件晶圆台、基板晶圆台以及镜面拾取和放置系统。该公司表示,机器会根据生产流程的需要自动更换基板和晶圆组件,且为实现高精度,公司发布了用于快速稳固高精度对准的光学硬件。

不过,裸片对准的探索仍未停止,往后可能会出现新的对准问题或缺陷,与所有封装一样,混合粘合的2.5D和3D封装可能需要经历更多的测试和检查步骤。

小结

混合键合是一项可行的技术,可能催生新一类产品。不过客户需要权衡其选择并深挖其中的细节,并不是一件容易的事情。

版权及免责声明:凡本网所属版权作品,转载时须获得授权并注明来源“物联之家 - 物联观察新视角,国内领先科技门户”,违者本网将保留追究其相关法律责任的权力。凡转载文章,不代表本网观点和立场。

延伸阅读

版权所有:物联之家 - 物联观察新视角,国内领先科技门户